7.2: Decoder Circuit

- Page ID

- 26989

The implementation of a decoder is based on the idea that all possible combinations of output from a given set of inputs can be generated by using AND operations on combinations of the input and inverted input bits. For example, for the two bits A and B all of the possible combinations of the bits are 00, 01, 10, and 11, or A'B', A'B, AB', and AB.

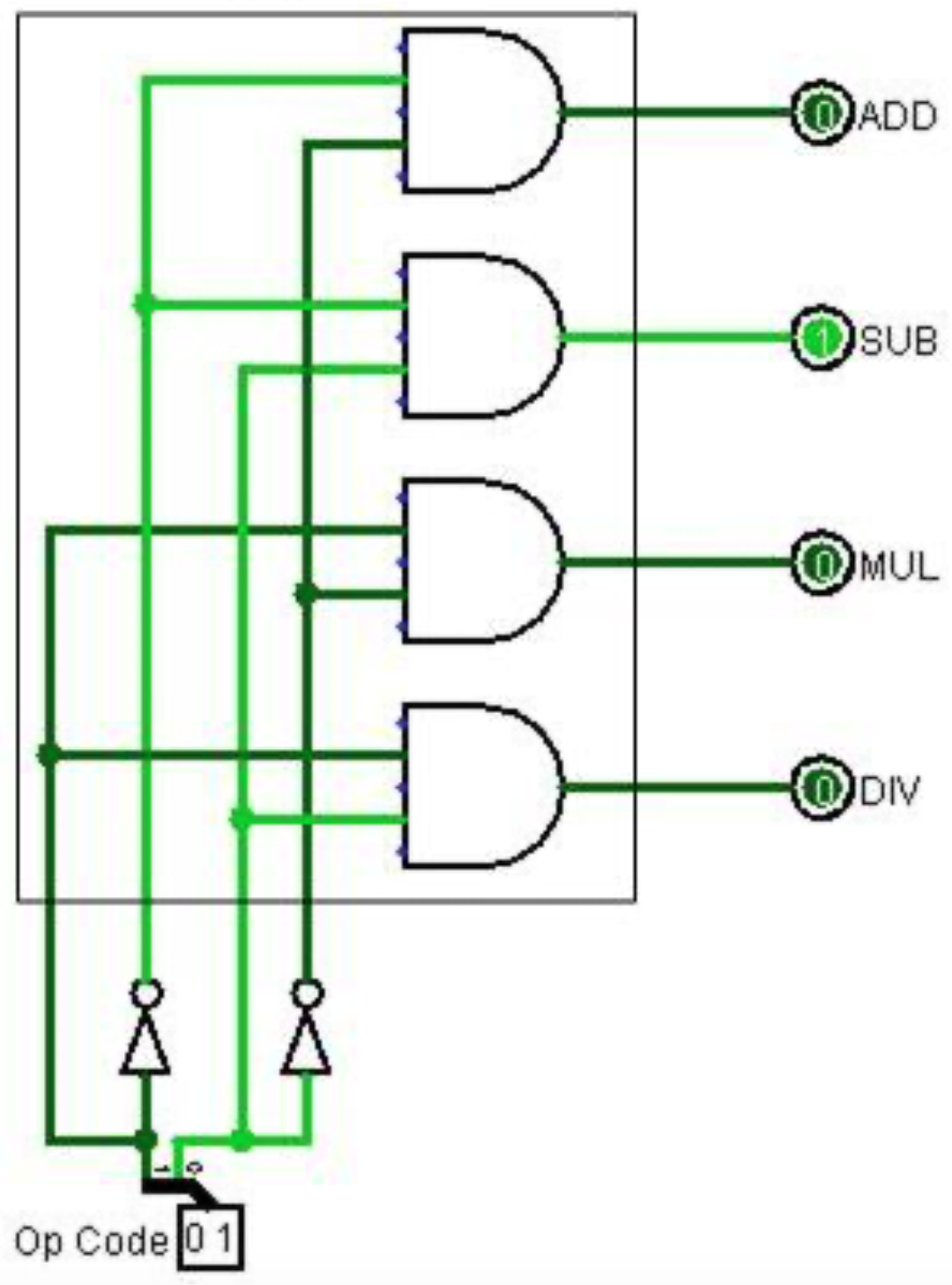

Consider the decoder in Figure 7.1.2, which has two inputs and 4 outputs. The implementation of this decoder is given in Figure \(\PageIndex{1}\). There are 2 inputs lines which are split into 4 lines, 2 normal and 2 inverted. These 4 lines are sent to 4 AND gates, each AND gate producing an output for one and only one value from the 2 input lines.

This shows a decoder is a circuit which enumerates all the values from the input bits by splitting them into separate output lines. A 3-to-8 decoder would have 3 input bits which would use AND and NOT gates to produce 8 output (000, 001, 010, 011, 100, 101, 110, and 111). The implementation of a 3-to-8 decoder is left as an exercise.