20.2: Interrupt Types and Levels

- Page ID

- 19989

Interrupts have various types and privileges associated with them. The following sections provide an explanation of the types and privileges. Interrupted processes may execute at a lower privilege than the interrupt processing code. In order for interrupts to be effective, the OS must securely handle this privilege escalation and deescalation securely and quickly.

Interrupt Types

The two different types or kinds of interrupts are:

- Maskable interrupts

- Non-maskable interrupts

Maskable interrupts are typically issued by I/O devices. As the name 'maskable' implies, maskable interrupts can be ignored, or masked, for a short time period. This allows the associated interrupt processing to be delayed.

Non-maskable interrupts (NMI's) must be handled immediately. This includes some OS functions and critical malfunctions such as hardware failures. Non-maskable interrupts are always processed by the CPU.

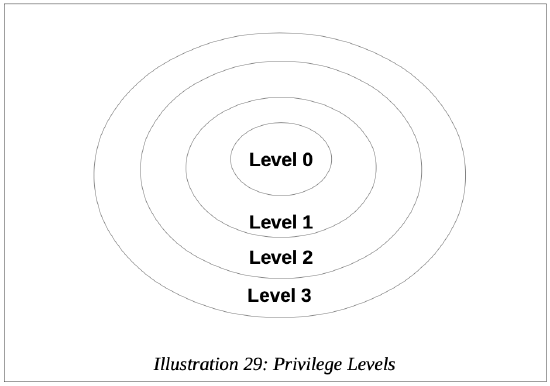

Privilege Levels

Privilege Levels refer to the privilege level at which the interrupt code executes. This may be a higher privilege level than the interrupted code is executing. The processor executes code in one of four privilege levels as follows:

|

Level |

Description |

|

Level 0 |

Full access to all hardware resources (no restrictions). Used by only the lowest level OS functions. |

|

Level 1 |

Somewhat restricted access to hardware resources. Used by library routines and software that interacts with hardware. |

|

Level 2 |

More restricted access to hardware resources. Used by library routines and software that has limited access to some hardware. |

|

Level 3 |

No direct access to hardware resources. Application programs run at this level. |

Should an application program executing at level 3 be interrupted by a hardware interrupt for the keyboard, the keyboard interrupt handler must execute at level 0.

The following diagram shows the relationship of the levels.

The operating system interrupt processing mechanism will handle this privilege elevation and restoration in a secure manner. That requires that the interrupt source and privileges be verified as part of the interrupt handling mechanism.