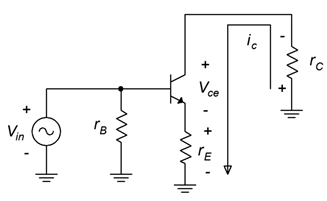

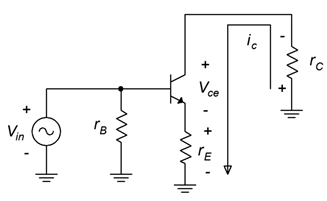

The signal current in the class A amplifier flows continuously throughout the entire cycle of the waveform. Ultimately, we would like to known just how large this signal can be before it is limited and grossly distorted. To do so, we need to examine the AC equivalent of the amplifier. A generic AC equivalent is shown in Figure \(\PageIndex{1}\). This includes both AC collector and emitter resistances so it can be used for either swamped or unswamped common emitter amplifiers or for emitter followers. If one of the resistances is not used (for example, \(r_C\) in a follower), we can just substitute a value of zero for it.

Figure \(\PageIndex{1}\): AC equivalent circuit.

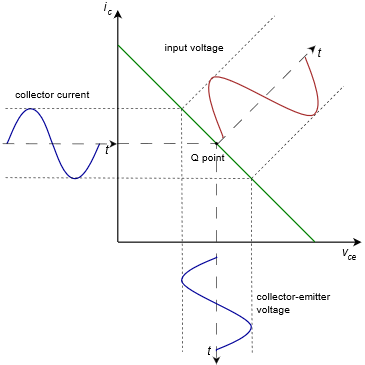

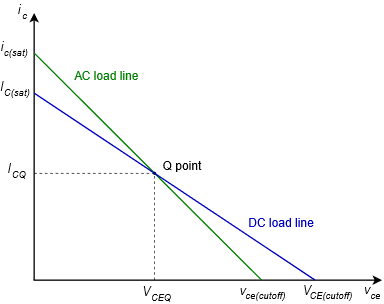

The voltage polarities and current direction are shown for a positive input voltage. To determine the maximum load voltage swing (compliance), we will need to construct an AC load line as shown in Figure \(\PageIndex{2}\).

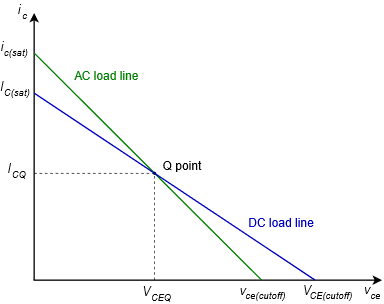

Figure \(\PageIndex{2}\): AC and DC load lines.

The AC load line is similar to the DC load line that was used for analyzing biasing circuits. As in the DC version, there will be a cutoff voltage, \(v_{CE(cutoff)}\), and a saturation current, \(i_{C(sat)}\). The AC and DC load lines normally are not the same, however, they must share one point in common, and that's the Q point. Usually, the slope of the AC load line is steeper than that of the DC load line. This is because the AC resistance tends to be less than the DC resistance due to loading and capacitor bypassing. Consequently, \(v_{CE(cutoff)}\) tends to be smaller than \(V_{CE(cutoff)}\) and \(i_{C(sat)}\) tends to be larger than \(I_{C(sat)}\).

To determine expressions for the AC load line endpoints, let's examine the AC equivalent circuit. Because both load lines share the Q point, we can consider the circuit of Figure \(\PageIndex{1}\) as having a no-signal current of \(I_{CQ}\) and a no-signal transistor voltage of \(V_{CEQ}\). As the input signal grows, \(i_C\) increases. The effect of this is to increase the voltage drops across \(r_E\) and \(r_C\) due to Ohm's law. This, in turn, forces \(v_{CE}\) to decrease due to KVL. The collector current can only increase to the point where \(v_{CE}\) drops to 0 V. This is a maximum increase of \(V_{CEQ}/(r_C+r_E)\). Therefore

\[i_{C(sat )} = I_{CQ} + \frac{V_{CEQ}}{r_E+r_C} \label{8.1} \]

In terms of cutoff voltage, the transistor starts with \(V_{CEQ}\) and \(I_{CQ}\). The largest \(v_{CE}\) increase that can occur is if the current falls to zero. Then, all of the potential originally developed across \(r_E\) and \(r_C\) by \(I_{CQ}\) must be absorbed by the transistor. Therefore

\[v_{CE (cutoff )} = V_{CEQ} +I_{CQ} (r_E+r_C ) \label{8.2} \]

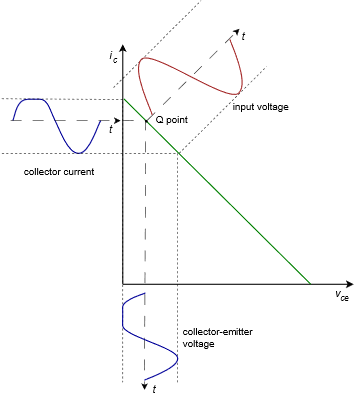

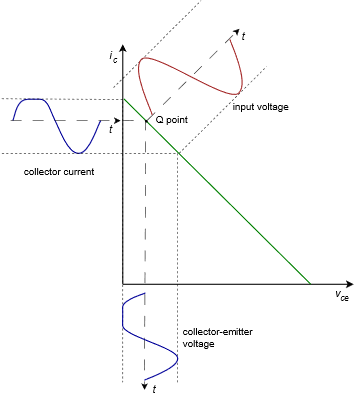

There are three possible ways this can be configured: Q point closer to saturation, Q point closer to cutoff, or Q point centered on the AC load line. Let's first consider the Q point closer to saturation. This is shown in Figure \(\PageIndex{3}\).

Here we have plotted the input voltage in red and drawn the corresponding collector current and collector-emitter voltage in blue. It is apparent that as the input signal increases, eventually, the output signal is limited at zero for \(v_{CE}\) and at \(i_{C(sat)}\) for \(i_C\). The two blue waveforms are severely clipped and distorted. The largest unclipped peak voltage swing is \(V_{CEQ}\) and the largest peak current swing is \(i_{C(sat)} − I_{CQ}\), or more conveniently, \(V_{CEQ}/(r_E+r_C)\).

Figure \(\PageIndex{3}\): AC load line, Q point closer to saturation.

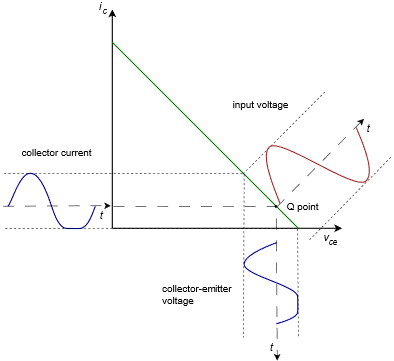

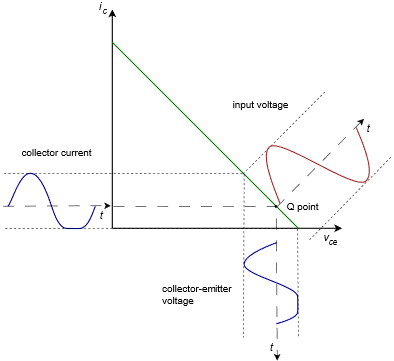

If we shift the Q point toward cutoff, we solve the saturation clipping problem but now we have a new problem, as illustrated in Figure \(\PageIndex{4}\). It should come as no surprise that we now have cutoff clipping.

Figure \(\PageIndex{4}\): AC load line, Q point closer to cutoff.

In this version the largest unclipped peak voltage swing is \(v_{CE(cutoff)} − V_{CEQ}\) (or alternately, \(I_{CQ}(r_E+r_C))\) and the largest peak current swing is \(I_{CQ}\). What's important here is that the waveform has been clipped. It doesn't really matter which side has been clipped, either way it's gross distortion. Eventually, every amplifier will have a limit but we will be able to produce the largest unclipped voltage swing if the Q point is centered on the AC load line. This is shown in Figure \(\PageIndex{5}\).

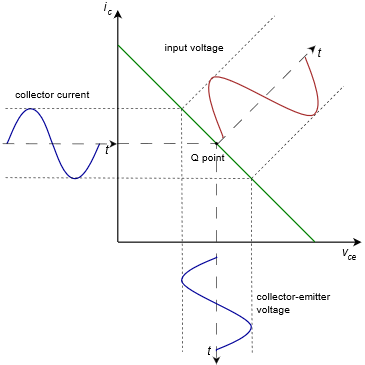

Figure \(\PageIndex{5}\): AC load line, centered Q point.

With a centered Q point, the largest unclipped peak voltage swing is \(V_{CEQ}\) and the largest unclipped peak current swing is \(I_{CQ}\). By examining equations \ref{8.1} and \ref{8.2} it is apparent that in order to achieve a centered Q point on the AC load line, the following must be true:

\[\frac{V_{CEQ}}{I_{CQ}} = r_E+r_C \label{8.3} \]

Of course, while it is useful to determine the maximum voltage across the transistor, it is more important to determine the maximum voltage across the load. Looking back at the circuit of Figure \(\PageIndex{1}\), most times the maximum load voltage (i.e., the compliance) will equal the maximum transistor voltage. This will be the case in voltage followers and unswamped amplifiers. The only time there will be a noticeable reduction is with very heavily swamped amplifiers. In this case the compliance will be reduced by the voltage divider between the load and swamping resistors. For example, a swamped amplifier with a voltage gain of 4 would lose about 20% of the maximum swing. Swamping has to be very heavy resulting in very low gains before appreciable signal is lost.

Thus we arrive at the following general rule:

\[\text{Peak compliance is the smaller of } V_{CEQ} \text{ or } I_{CQ}(r_E+r_C) \label{8.4} \]

Knowing the compliance, the maximum load power may be determined using power law. Power is determined using RMS values, so the peak compliance will need to be divided by \(\sqrt{2}\) (or multiplied by 0.707) before continuing.

\[P_{load (max)} = \frac{{Compliance_{RMS}}^2}{R_L} \label{8.5} \]

There is something important to note about this equation. It uses the load resistance value, not the total AC effective value (i.e., not \(r_L\) which is \(R_L\) in parallel with a biasing resistor). If \(r_L\) was used, we'd be calculating the power in the load plus the power in the biasing resistor.

We would also like to determine the maximum power dissipated by the transistor. Because the transistor's current and voltage are fluctuating with the input signal, we need to determine the magnitude of the load voltage that produces maximum power in the transistor. Intuitively, we might guess that this occurs at maximum load power but it turns out that this guess is incorrect. Under no-signal conditions the transistor is operating statically at the Q point. Therefore, quiescent power dissipation is

\[P_{DQ} = V_{CEQ} I_{CQ} \label{8.6} \]

In contrast, at full load for a centered Q point, we have

\[v_{CE} = V_{CEQ} (1− \sin 2 \pi ft) \nonumber \]

\[i_C = I_{CQ} (1+ \sin 2 \pi ft) \nonumber \]

\[P_D = v_{CE} i_C \\ P_D = V_{CEQ} (1− \sin 2 \pi ft) \times I_{CQ} (1+ \sin 2 \pi ft) \\ P_D = V_{CEQ} I_{CQ} (1− \sin^2 2 \pi ft) \\ P_D = V_{CEQ} I_{CQ} (.5+.5 \cos 4 \pi ft) \\ P_D = \frac{P_{DQ}}{2} + \frac{P_{DQ}}{2} \cos 4 \pi ft \label{8.7} \]

The first term of Equation \ref{8.7} is a fixed offset while the second term is a sinusoid at twice the signal frequency. Because the peak amplitude of this sinusoid is the same as the fixed offset, the average over time is simply the offset value. These waveforms are illustrated in Figure \(\PageIndex{6}\).

Figure \(\PageIndex{6}\): Transistor power dissipation at full load power.

The result is that the transistor only dissipates half the power at full load that it dissipates under idle conditions. This makes perfect sense if you stop to consider that the class A amplifier always draws the same power from the DC supplies, regardless of the size of the load signal. Without clipping, the average current will be \(I_{CQ}\). That current times the supply voltage yields the supplied power. What's happening is that as the signal increases in amplitude, more and more of the power dissipated by the transistor is shifted to the load. At maximum load swing, both the transistor and the load will be dissipating \(P_{DQ}/2\). As strange as it might seem, if you want to keep the output transistor of a class A amplifier cool, don't turn the volume down, turn it up.

The foregoing implies that class A designs are not power efficient. This is indeed the situation. As we have just seen, the best case maximum load power will be one half of \(P_{DQ}\), assuming a centered Q point (non-centered will be worse). To achieve this swing, the power supply will have to be at least twice as large as \(V_{CEQ}\) because it has to cover the peak-to-peak swing, while \(V_{CEQ}\) represents the peak swing for a centered Q point.1 In any event, the best case efficiency turns out to be dismal, as follows.

\[\eta = \frac{P_{out}}{P_{i n}} = \frac{P_{load}}{P_{DC}} \nonumber \]

\[\eta = \frac{P_{DQ} /2}{2V_{CEQ} I_{CQ}} \nonumber \]

\[\eta = \frac{P_{DQ} / 2}{2 P_{DQ}} \nonumber \]

\[\eta = 25 \% \nonumber \]

This represents the maximum or best case efficiency for an \(RC\) coupled class A amplifier. It may be considerably less depending on precisely how it is biased. This, truly, is the Achilles heel of the class A topology: it is wasteful. It draws full power from the supply regardless if signal is present and, at best, will translate only one quarter of that power into useful load power. At the same time, the power dissipation of the transistor will need to be at least twice that of the delivered load power, and might need to be much greater. Why use it then? To its advantage, it is a relatively simple design so if large output powers are not needed, it can prove useful. This is most definitely the case for the early stages of a multi-stage amplifier where the amount of load power is very small (basically the power delivered to the following stage). In that instance, the increased complexity of more power efficient designs is not warranted or cost effective.

Example \(\PageIndex{1}\)

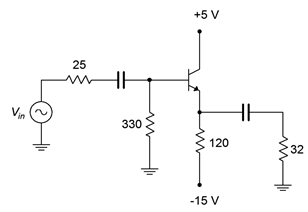

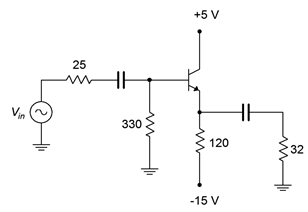

For the amplifier shown in Figure \(\PageIndex{7}\), determine the compliance, maximum load power, worst case transistor dissipation and efficiency.

Figure \(\PageIndex{7}\): Schematic for Example \(\PageIndex{1}\).

\[I_{CQ} = \frac{∣V_{EE}∣−V_{BE}}{R_E} \nonumber \]

\[I_{CQ} = \frac{15 V−0.7 V}{120 \Omega} \nonumber \]

\[I_{CQ} = 119mA \nonumber \]

By inspection, \(V_{CEQ}\) = 5.7 V. The AC cutoff voltage is

\[v_{CE (cutoff )} = V_{CEQ} +I_{CQ} (r_C+r_E ) \nonumber \]

\[v_{CE (cutoff )} = 5.7 V+119mA(0+120 \Omega || 32 \Omega ) \nonumber \]

\[v_{CE (cutoff )} = 5.7 V+119mA(25.3 \Omega ) \nonumber \]

\[v_{CE (cutoff )} = 5.7 V+3V \nonumber \]

\[v_{CE (cutoff )} = 8.7 V \nonumber \]

The smaller of \(V_{CEQ}\) and \(I_{CQ}(r_C+r_E)\) is the peak compliance, so

\[compliance = 3 V peak \nonumber \]

Given the compliance, we can use power law to find the load power

\[P_{load (max)} = \frac{{Compliance_{RMS}}^2}{R_L} \nonumber \]

\[P_{load (max)} = \frac{(.707 \times 3 V)^2}{32 \Omega} \nonumber \]

\[P_{load (max)} = 141mW \nonumber \]

This is not a lot of power for something like a loudspeaker but is a fair amount to drive something like a pair of headphones.

The transistor's worst case power dissipation is

\[P_{D (max)} = P_{DQ} = I_{CQ} V_{CEQ} \nonumber \]

\[P_{D (max)} = 119mA \times 5.7V \nonumber \]

\[P_{D (max)} = 678mW \nonumber \]

The supplied circuit power is the average current draw times the total supplied voltage differential

\[P_{DC} = I_{CQ} (V_{CC} −V_{EE}) \nonumber \]

\[P_{DC} = 119mA \times 20 V \nonumber \]

\[P_{DC} = 2.38W \nonumber \]

The efficiency is the ratio of maximum load power to supplied DC power

\[\eta = \frac{P_{load (max )}}{P_{DC}} \nonumber \]

\[\eta = \frac{141mW}{2.38 W} \nonumber \]

\[\eta = 5.9 \% \nonumber \]

This is much worse than the theoretical best case. This is due, at least in part, to the fact that the Q point is not centered on the AC load line.

To complete the analysis, note that the transistor's breakdown rating (\(BV_{CEO}\)) should be at least as large as \(v_{CE(cutoff)}\) (8.7 volts), and the maximum current rating should be at least as large as \(i_{C(sat)}\) (119 mA+5.7 V/25.3 \( \Omega \) = 344 mA).

Computer Simulation

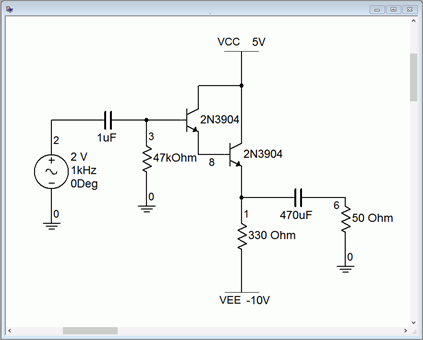

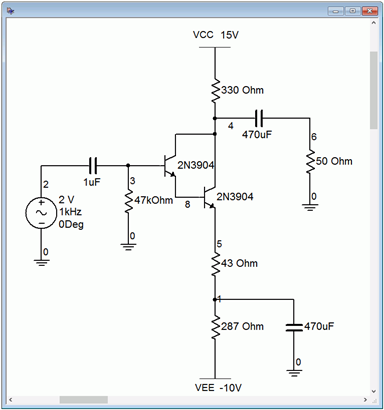

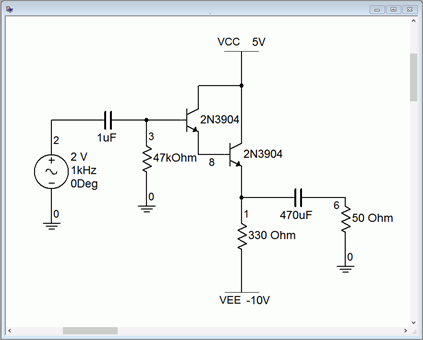

A computer simulation of a class A emitter follower using a Darlington pair is examined next. Of primary interest here is the verification of the output compliance so a transient analysis will be used. The simulator schematic is shown in Figure \(\PageIndex{8}\).

Figure \(\PageIndex{8}\): Class A follower in simulator.

We can make a few quick computations to determine the compliance. First, we find the collector Q point current.

\[I_{CQ} = \frac{∣V_{EE}∣−V_{BE}}{R_E} \nonumber \]

\[I_{CQ} = \frac{10 V−1.4 V}{330 \Omega} \nonumber \]

\[I_{CQ} = 26mA \nonumber \]

By inspection, the emitter is two base-emitter junction potentials below ground, or −1.4 V. As the collectors are tied to \(V_{CC}\), this means that \(V_{CEQ}\) = 6.4 V. The other half of the swing, from \(V_{CEQ}\) to \(v_{CE(cutoff)}\) is

\[v_{CE (cutoff )}−V_{CEQ} = I_{CQ}(r_C+r_E ) \nonumber \]

\[v_{CE (cutoff )}−V_{CEQ} = 26mA(0+330 \Omega || 50 \Omega ) \nonumber \]

\[v_{CE (cutoff )}−V_{CEQ} = 26mA( 43.4 \Omega ) \nonumber \]

\[v_{CE (cutoff )}−V_{CEQ} = 1.13V \nonumber \]

The Q point is not centered and is closer to cutoff. This means that the amplifier will produce cutoff clipping around 1.1 volts and saturation clipping around 6 volts. In other words, there is more room for the current to swing up to saturation than to swing down to zero. As this is the current flowing through the load and we have a non-inverting follower, we expect to see the load voltage echo this. That is, the negative portion of the load voltage should clip before the positive portion.

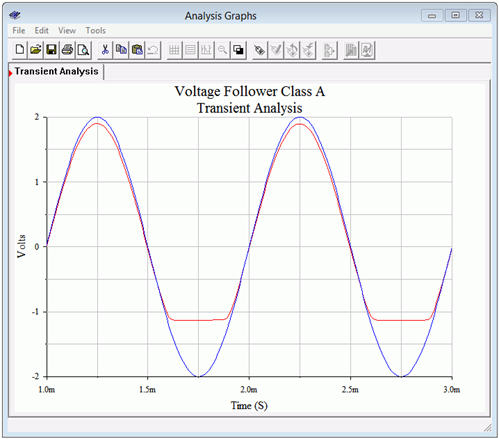

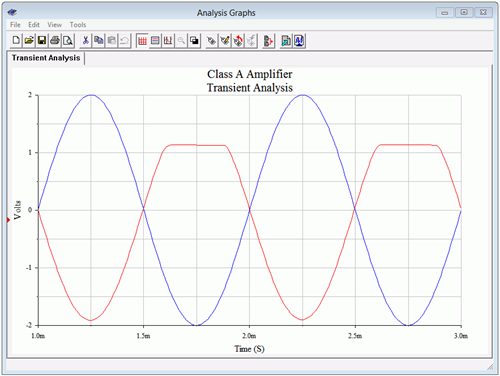

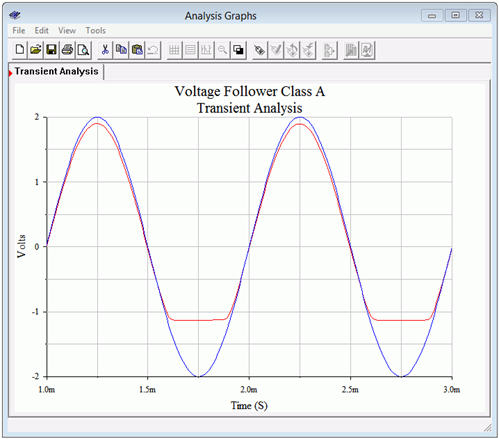

The transient analysis results are shown in Figure \(\PageIndex{9}\). A two volt peak input signal is applied (blue trace). The negative portion of the load voltage clips at approximately 1.1 volts as expected (red trace). The input signal is not large enough to cause saturation clipping. This was done on purpose to verify the voltage gain of the follower. It should be very close to unity. In fact, the trace shows that the gain is around 0.95 or so.

Figure \(\PageIndex{9}\): Class A follower transient analysis.

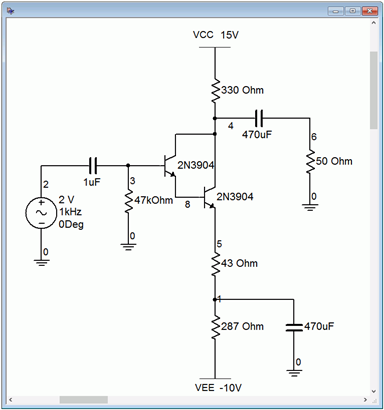

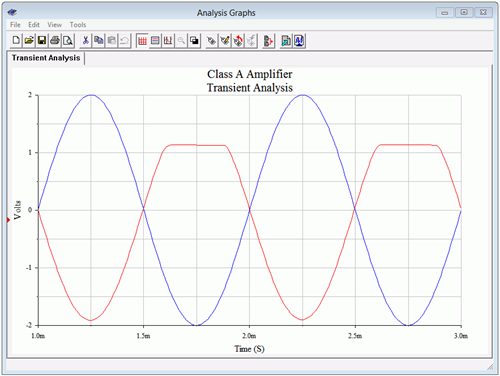

If this had been a voltage amplifier instead of a follower, these waveforms would appear flipped vertically. To verify this, the circuit is modified to produce a voltage amplifier with a gain of approximately one. This is achieved by moving the load to the collector and adding a 330 \( \Omega \) biasing resistor. This will result in the same AC load impedance. To maintain a similar \(V_{CEQ}\), \(V_{CC}\) is raised by 10 volts. Finally, the original 330 \( \Omega \) emitter biasing resistor is split in two: 287 \( \Omega \) and 43 \( \Omega \). This will yield the same \(I_{CQ}\) and achieve a voltage gain of unity. As a result, we expect to see clipping at approximately 1.1 volts on the positive portion. The modified circuit is shown in Figure \(\PageIndex{10}\) and the resulting transient simulation in Figure \(\PageIndex{11}\).

Figure \(\PageIndex{10}\): Class A amplifier in simulator.

Figure \(\PageIndex{11}\): Class A amplifier transient analysis.

One final item of interest regarding the simulations: If the input level is increased in an attempt to see clipping on the other half of the waveform, something strange happens. At first it will appear as though it never clips. A careful examination reveals something different, though. Given the values in these circuits, they will exhibit a certain amount of clamping action (clamping was presented in Chapter 3). This will cause the waveform to shift. If you inspect the peak-to-peak value, it will be close to the value of \(v_{CE(cutoff)}\). It will be a little less due to the fact that, particularly for a Darlington pair, \(V_{CE(sat)}\) is not 0 V.

References

1This is the case if the AC and DC load lines are identical. This is atypical. Consequently, the power supply will tend to be larger than twice \(V_{CEQ}\) which makes the situation even worse.