5.1: Abstract MSCPU

- Page ID

- 76114

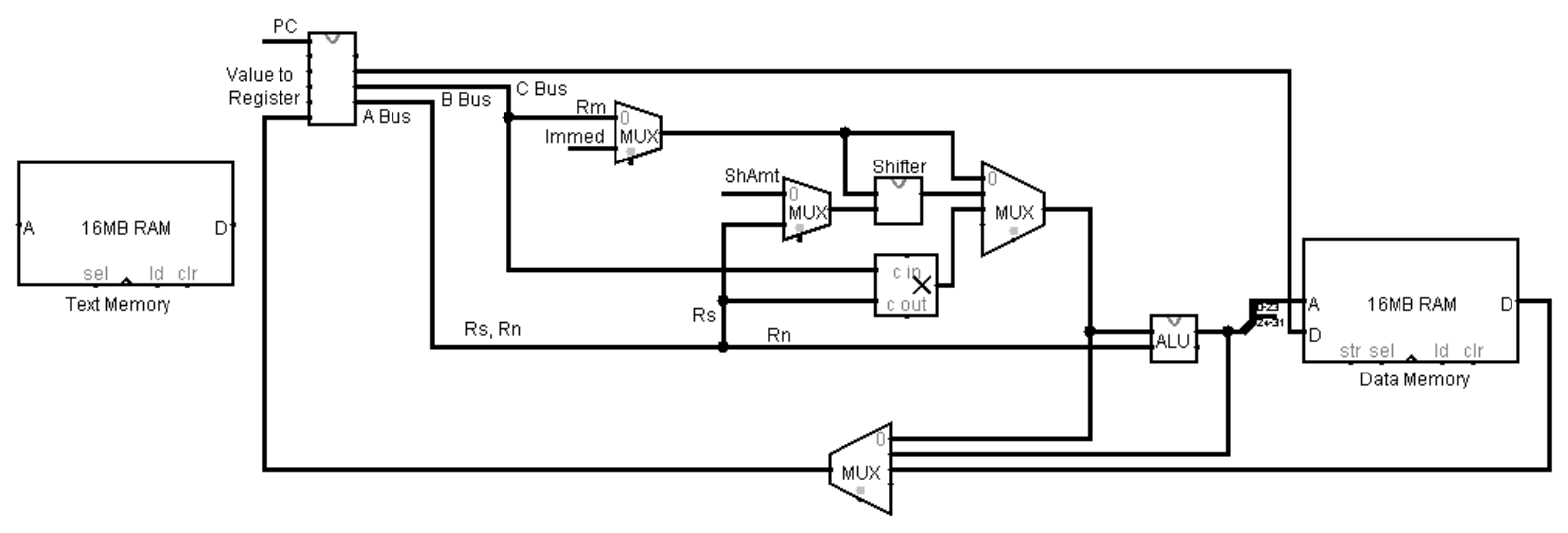

The following is an abstract view of an ARM-like CPU that implements the flexible operand, or Operand2, of the ARM CPU, and will be called the MSCPU.

Figure 23: MSCPU

The MSCPU differs from the 3-Address Load and Store CPU in that two new operational units, the multiplier and the barrel shifter, are added to the CPU to do computation before the values are passed to the ALU. These new units allow the CPU to include the Multiply and Accumulate (mla) instruction and the Operand2.

This abstract CPU is also developed using Logisim rather than a drawing tool, as the complexity of the drawing is such that it is easier to implement the CPU in a circuit simulation tool, such as Logisim, than to try to draw it abstractly. Using Logisim results in some differences, like including a multiplexer (mux) to select between inputs. The reader can think of a mux as a unit to select which of 2 or more inputs is forwarded to the output. For example, the mux on the B bus (the mux with the Rm and immed inputs at the top center of the diagram) selects if a register, Rm, or an immediate value is sent forward.

A third difference between the 3-address CPU and the MSCPU is that there is now another bus, the C bus. In the MSCPU, the 3 buses have the following usages.

- The A bus runs to three places: the mux to select the bottom input of the barrel shifter; the bottom input to the multiplier; or the bottom input to the ALU. This bus will have either Rn, Rs, or ShAmt on it.

- The B bus runs to a mux that selects between the register value, always Rm, and an immediate value. The B bus then runs to three places: the top input of the barrel shifter; the top input to the multiplier; and a multiplexer that chooses what data to send to the top input of the ALU.

- The C bus is used for the store operation to transfer the data from a register to the data memory.

The final modification is that some of the MSCPU instructions will take 2 clock cycles to run. In the parlance of CPU design, this means the CPU has a Cycles Per Instruction (CPI) of 2. All of the 3-address instructions will still have a CPI=1 as they will use only one of the units (e.g., the multiply unit, the barrel shifter, or the ALU). Only the MLA and instructions using the Operand2 will have a CPI=2 as these operations will require 2 cycles, one for the multiplier and shifter, and the other for subsequently using the ALU. This will be explained using the datapath for the instructions in the section below.